signo X y Y, y una señal de control MIN/MAX. La salida del circuito es un binario entero de 8 bits sin signo Z, tal que Z=0 si X=Y; de otra forma Z=Min(X,Y), si MIN/MAX=1 y Z=max(X,Y) si MIN/MAX=0.

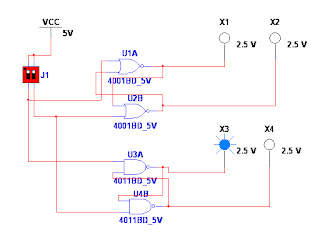

En la siguiente Figura se muestra la tabla de verdad tanto para el latch S-R con compuertas NAND y NOR.

Tabla de verdad para latch S-R.

Para S=0 y R=1. Donde se puede observar que si cumple con los valores de la tabla cuando se aplica el latch con compuertas NOR y NAND.

A continuación se muestra la comprobación de la tabla de verdad.

Para S=1 y R=0. Donde se puede observar que es lo contrario a estado anterior si cumple con los valores de la tabla cuando se aplica el latch con compuertas NOR y NAND.

No hay comentarios:

Publicar un comentario